Find and double click on “ZYNQ7 Processing System”.

#WHAT IS PCI EXPRESS ROOT COMPLEX DRIVER ZIP#

#WHAT IS PCI EXPRESS ROOT COMPLEX DRIVER DOWNLOAD#

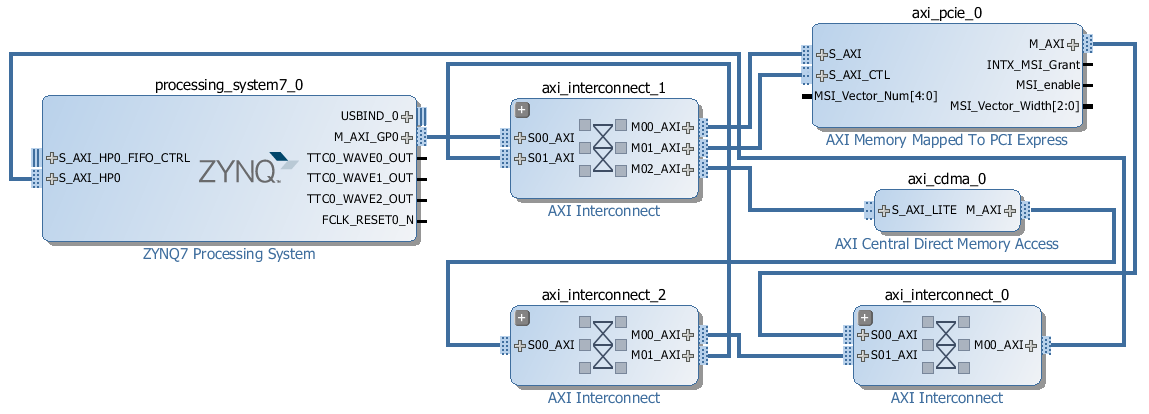

the CDMA can access both the DDR3 memory and the PCIe address space.the PCIe end-point with bus mastering capability can access the DDR3 memory only (via M_AXI port of the AXI-PCIe bridge).the Zynq PS can access both the DDR3 memory and the PCIe address space.So again let’s look at who the bus masters are and what address spaces they can access: The reason is that a lot of the elements required in this design are hidden in the Zynq PS block, including the DDR3 memory controller, UART, Ethernet, Interrupt controller, Timer and QSPI. If you went through the previous tutorial where we created the same design for a Microblaze system, you may be wondering why the Zynq design seems so much simpler.

It shows three main elements: the Zynq PS, the AXI to PCIe bridge and the AXI CDMA. The diagram below shows the block design we are about to build with only the AXI interfaces showing. Note: The tutorial text and screenshots are suitable for Vivado 2015.4 however the sources in the Git repository will be regularly updated to the latest version of Vivado. A JTAG programmer such as Digilent HS3 JTAG.An NVMe PCIe solid-state drive such as this one.To complete this tutorial you will need the following: We will then run PetaLinux on the FPGA and prepare our SSD for use under the operating system. In part 3, we will then test the design on the target hardware by running a stand-alone application which will validate the state of the PCIe link and perform enumeration of the PCIe end-points. In this second part of the tutorial series, we will build a Zynq based design targeting the PicoZed 7Z030 and PicoZed FMC Carrier Card V2. Part 3: Connecting an SSD to an FPGA running PetaLinux Part 2: Zynq PCI Express Root Complex design in Vivado (this tutorial) Part 1: Microblaze PCI Express Root Complex design in Vivado

0 kommentar(er)

0 kommentar(er)